Informatics Point

Информатика и проектирование

Выбор элементной базы

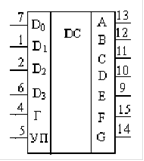

Для преобразования кода импульсов на выходах триггеров в цифро-буквенные значения используется дешифратор 514ИД4А (рис 2.4).

Рисунок 2.4 - Условное графическое обозначение дешифратора 514ИД4А

Дешифраторы 4-разрядного двоичного кода в сигналы 7-сегментного кода. Выпускаются в металлостеклянном корпусе. При эксплуатации крепятся к радиатору с тепловым сопротивлением не более 20°С/Вт.

Предназначены для управления полупроводниковыми 7-сегментными цифро-буквенными индикаторами на основе светодиодных структур с разъемными анодами.

Обозначение выводов:0-D3-информационные входы, предназначенные для приема 4-разрядного двоичного слова;

Г - вход гашения;

УП - вход управления памятью;, B, C, D, E, F, G - выходы, подключаемые к анодам сегментов индикатора;

-Uпит;

-общий.

Дешифрирование входных сигналов осуществляется при установлении низких логических уровней на входах Г и УП. При указанных условиях микросхема функционирует по следующему логическому закону соответствия входной (на выводах D3, D2, D1, D0) и выходной (на выводах A, B, C, D, E, F, G) информации (в скобках указывается соответствующий символ, индицируемый индикатором):

-1111110 (0), 0001-0110000 (1), 0010-1101101 (2),

-1111001 (3), 0100-0110011 (4), 0101-1011011 (5),

-1011111 (6), 0111-1110000 (7), 1000-1111111 (8),

-1111011 (9), 1010-1110111 (A), 1011-0011111 (B),

-1001110 (C), 1101-0111101 (D), 1110-1001111 (E),

-1000111 (F).

Сигнал высокого логического уровня, поступающий на вход Г, переводит все выходы дешифратора в состояние логических нулей, при этом все сегменты индикатора гаснут.

Основные параметры дешифратора 514ИД4А при Т=25°С приведены в таблице 2.4

Таблица 2.4 - Электрические параметры дешифратора 514ИД4А

|

Параметр |

Значение |

|

I0вх (при Uвх=0,4 В),мкА |

800 |

|

I1вх (при Uвх=2,4 В),мкА |

40 |

|

I0вых (при Uвых=1,25 В),мкА |

200 |

|

I1вых (при Uвых=1,7 В),мА |

13 |

|

I1вых (при Uвых=3 В),мА |

7 |

|

Iпот (при выключенных сегментах индикатора),мА |

60 |

Построение схемы

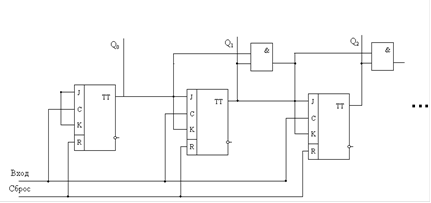

Функциональная схема синхронного суммирующего счетчика представлена на рис 3.1.

Рисунок 3.1 - Схема синхронного суммирующего счетчика (для n-разрядов)

Составим таблицу истинности для цепи переноса и логическое выражение для функции i-го рода.

Таблица 3.1-Таблица истинности для цепи переноса

|

ai |

Pi |

Ci |

Pi+1 |

|

0 |

0 |

0 |

0 |

|

0 |

1 |

1 |

0 |

|

1 |

0 |

1 |

0 |

|

1 |

1 |

0 |

1 |

i - цифра i-го разрядаi - сигнал переноса, который поступает из i-1 в i-й разрядi - последующая цифра i-го разрядаi+1 - сигнал переноса, поступающий в более старший разряд)

Лучшие статьи по информатике

Программно управляемый генератор сигнала типа меандр сверхнизкой частоты на микроконтроллере

является

8-ми разрядным CMOS микроконтроллером с низким уровнем энергопотребления,

основанным на усовершенствованной AVR RISC архитектуре. Благодаря выполне ...

Проект цифрового печатного узла, выполняющего функцию стабилизации напряжения

Производство

цифровых устройств электронной аппаратуры в настоящее время находит все более

широкое применение во многих областях народного хозяйства и в зна ...

Разработка автоматизированной системы контроля процессов пайки топливных коллекторов

На современном этапе развития промышленности, обеспечение стабильной

работы предприятий по выпуску конкурентоспособной продукции, является задачей

первостеп ...

Меню сайта

- Главная

- Проектирование современных устройств

- Разработка схем цифровых устройств

- Современные датчики положения

- Современные сетевые технологии

- Современные системы видеонаблюдения

- Телекоммуникационные системы в гостиницах

2026 © www.informaticspoint.ru