Informatics Point

Информатика и проектирование

Суммирующий синхронный счетчик

В наше время проявляется тенденция к бурному развитию цифровой электроники. Курсовая работа предполагает рассмотрение и разработку такого устройства цифровой электроники как суммирующий синхронный счетчик.

Счетчики получили очень широкое распространение в самых различных отраслях промышленности, в быту, в повседневной жизни, потому что они являются многофункциональными устройствами.

Эти устройства используются не только для подсчета импульсов, поданных на вход, но и для деления входной частоты с заданным коэффициентом деления.

Актуальность проектирования подобного вида устройств заключается в том, что они обладают высоким быстродействием, приемлимой помехоустойчивостью, низкой потребляемой мощностью, относительно низкой стоимостью.

Счетчики могут применяться в качестве счетчиков каких-либо изделий на производстве, в роли счетчика частиц (например, фотонов) и даже в самых обыкновенных электронных часах используются счетчики.

Аналитический обзор

Счетчиком называется устройство, предназначенное для подсчета числа импульсов, поданных на вход. Число разрешенных состояний счетчика называют его модулем или коэффициентом счета Ксч.

Используется множество различных вариантов счетчиков: асинхронный и синхронный; двоичные и десятичные; однонаправленные (с увеличением счета) и двунаправленные (с увеличением или уменьшением счета), называемые реверсивными, с постоянным или переключаемым коэффициентом деления. Основа любого счетчика является линейка из нескольких триггеров. Между триггерами могут быть введены дополнительные обратные связи, позволяющие получить любой коэффициент деления, а не только равный 2n. Например, счетчик, состоящий из четырех триггеров, может иметь максимальный коэффициент деления 24=16.

Для четырехтриггерного счетчика минимальный выходной код - 0000, максимальный - 1111, а при коэффициенте деления КД=10 выходной счет останавливается при коде 1001=9.

Следовательно, удобно выпускать четырехтригерные счетчики в двух вариантах: двоичном и десятичном. Расширить функции счетчиков можно, видоизменяя их цепи управления и вводя дополнительные связи между триггерами.

Основными временными характеристиками счетчиков являются максимальная частота поступления счетных импульсов fсч и время перехода из одного состояния в другое.

По характеру операций счета счетчики делятся на суммирующие, вычитающие и реверсивные. В зависимости от основания системы счисления, в которой осуществляется счет, они могут быть двоичными, двоично-десятичными, двоично-пятеричными и т.д. По схемным признакам счетчики могут быть асинхронными и синхронными.

В асинхронных счетчиках на тактирующие входы синхронных триггеров или на информационные входы асинхронных триггеров информация поступает с выходов соседних триггеров, поэтому триггеры в таких схемах срабатывают не одновременно, а последовательно, друг за другом. В синхронных счетчиках все триггеры переключаются одновременно под действием общего синхронизирующего сигнала, поступающие на тактирующие входы всех триггеров одновременно.

По способу организации цепей переноса они делятся на схемы с последовательным, параллельным и групповым переносом.

В счетчиках с последовательным переносом перенос в соседний старший разряд формируется только после переключения триггера в предыдущем разряде. Их быстродействие определяется суммой времен установления (задержки) триггеров всех разрядов.

В счетчиках с параллельным переносом аргументами функций переносов для каждого разряда являются только сигналы на выходах триггеров соответствующих сигналов, причем переносы для всех разрядов счетчика формируются одновременно. Их быстродействие определяется временем установки одного триггера и одной комбинационной схемы независимо от числа разрядов счетчика.

Цепи сквозного переноса организуются таким образом, чтобы функция переноса i-го разряда счетчика являлась аргументом функции переноса (i+1)-го разряда. В этом случае сигналы переносов для каждого разряда формируются поочередно, начиная с младших разрядов счетчика. Счетчики со сквозным переносом требуют меньшего числа логических элементов для организации цепей переноса, но уступают счетчикам с параллельным переносом в быстродействии. Их быстродействие определяется в худшем случае переключением n логических схем в цепях сквозного переноса и одного триггера (n - число разрядов счетчика).

Если счет выполняется в канонической двоичной системе счисления (в однородной позиционной двоичной системе счисления с естественным порядком весов), то такой счетчик называют с естественным порядком счета. Коэффициент счета при этом может быть Ксч≤2n, но независимо от его значения счет выполняется от 0 до Ксч.

Если счет выполняется в неканонических системах (например, символических, с искусственным порядком весов и т.д.), то порядок счета считается искусственным (произвольным).

В счетчиках Ксч ≠2n и произвольным порядком счета наиболее часто применяются схемы с принудительным насчетом и с начальной установкой.

Счетчики, выполненные в виде отдельных функциональных узлов, имеются в составе многих серий микросхем. Номенклатуру счетчиков отличает большое многообразие. Многие из них обладают универсальными свойствами и позволяют управлять коэффициентом и направлением счета, вводить до начала цикла исходное число, прекращать по команде счет, наращивать число разрядов и т.п.

В ряде случаев, однако, может возникнуть необходимость в счетчике с нетиповыми характеристиками. Такие счетчики синтезируются из отдельных триггеров и логических элементов.

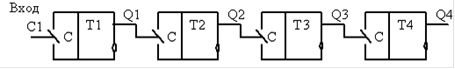

Простейший двоичный счетчик может быть реализован путем последовательного соединения счетных Т-триггеров (рис. 1.1).

Рисунок 1.1 - Двоичный суммирующий счетчик с последовательным переносом

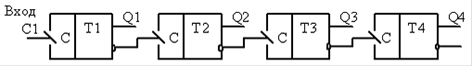

При построении временных диаграмм учитывалось, что каждый триггер изменяет свое состояние по спадающему фронту «1-0» на своем синхровходе. Логические уровни на выходах триггеров соответствуют двоичным числам, которые возрастают с приходом каждого входного импульса. Это объясняет название: «суммирующий двоичный счетчик».

Из временных диаграмм следует, что частота на выходе каждого триггера уменьшается в два раза. Поэтому двоичные счетчики называют также делителями частоты. Общий коэффициент деления равен:

![]() ,

,

где: n - количество последовательно включенных триггеров.

На основе Т-триггеров можно построить вычитающий двоичный счетчик, если на вход следующего триггера подавать сигналы с инверсного выхода предыдущего триггера. Вычитающий двоичный счетчик можно реализовать также по схеме на рис.1.2, если использовать Т-триггеры, управляемые восходящим фронтом «0-1».

Рисунок 1.2-Вычитающий двоичный счетчик с последовательным переносом

Логические уровни на выходах триггеров (см. временные диаграммы на рис.1.3) соответствуют двоичным числам, которые уменьшаются с приходом каждого входного импульса. Из нулевого состояния счетчик переходит - в максимальное (для четырехразрядного счетчика - это код 15).

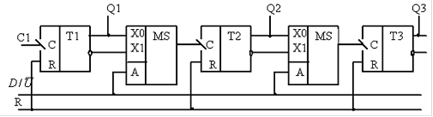

На рис. 1.4 приведен фрагмент реверсивного счетчика. Этот счетчик может работать как суммирующий при подаче на управляющий вход «D/~U» низкого логического уровня или как вычитающий, если подать на управляющий вход высокий логический уровень.

Рисунок 1.3 - Временные диаграммы двоичного вычитающего счетчика

Переключение режимов реверсивного счетчика осуществляется мультиплексорами «2 на 1».

В большинстве случаев счетчики имеют цепи установки всех триггеров в исходное состояние.

Рисунок 1.4-Реверсивный двоичный счетчик с последовательным переносом

Общим недостатком всех счетчиков с последовательным переносом (в литературе встречается также название «асинхронные счетчики») являются большие и неравномерные задержки распространения входного сигнала до всех выходов триггеров. Особенно большие задержки распространения сигнала заметны на выходе последнего триггера.

Если выходные логические уровни триггеров подать на входы дешифратора, то на выходах дешифратора будут заметны «ложные импульсы» (за счет эффекта гонок) длительностью до 12*tз и более.

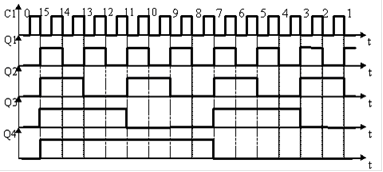

Для выравнивания временных задержек всех триггеров применяют счетчики с параллельным переносом (рис.1.5), которые называются также «синхронными счетчиками», потому что входной сигнал С подают параллельно на синхровходы всех триггеров.

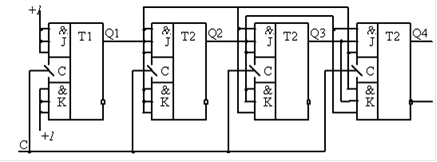

Рисунок 1.5-Двоичный суммирующий счетчик с параллельным переносом

Синхронный счетчик реализован на J-K-триггерах, имеющих по три входа J и три входа К, объединенных логической операцией конъюнкции.

Временные диаграммы этого счетчика такие же, как на рис.1.3. Первый триггер работает в счетном режиме. Для этого на его входы J и K постоянно поданы уровни логической «1».

Второй триггер изменяет (инвертирует) свое состояние по фронту «1-0» входного сигнала только при единичном уровне на выходе Q1.

Третий триггер изменяет свое состояние по фронту «1-0» входного сигнала С только при единичных уровнях на выходах первого и второго триггера. Четвертый триггер изменяет свое состояние, когда три первых триггера находятся в единичном состоянии. Поэтому на входы J, K последнего триггера поданы выходные сигналы первых трех триггеров.

Все триггеры могут изменять свои состояния только одновременно по фронту «1-0» входного сигнала. Поэтому задержки распространения сигналов на всех выходах будут примерно равны (если не считать технологический разброс параметров триггеров). Такой счетчик обладает минимальными задержками распространения сигналов от входа С ко всем выходам и поэтому - максимальным быстродействием.

Лучшие статьи по информатике

Технология спутникового и эфирного телевидения на основе предприятия ООО Антенн-Сервис

антенна сеть

В связи с быстрым развитием технологий и научных открытий всё более

актуальной становится проблема недостачности информации. Одним из средств

пе ...

Техническое обслуживание и ремонт Автомагнитолы JVC

Ни один автолюбитель не откажется от поездки в авто под хорошую

музыку. Современный водитель покупает автомагнитолу не в качества

доп ...

Элементная база для построения цифровых систем управления

Микроэлектроника - это комплексная область знаний, объектом изучения и

разработки которой являются функционально сложные ИС, их структура, технология,

диагн ...

Меню сайта

- Главная

- Проектирование современных устройств

- Разработка схем цифровых устройств

- Современные датчики положения

- Современные сетевые технологии

- Современные системы видеонаблюдения

- Телекоммуникационные системы в гостиницах

2026 © www.informaticspoint.ru