Informatics Point

Информатика и проектирование

Расчёт базового элемента

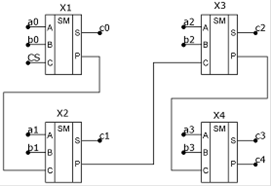

Последовательным соединением получаем 4-битный сумматор:

Рис. 5. 4-битный сумматор

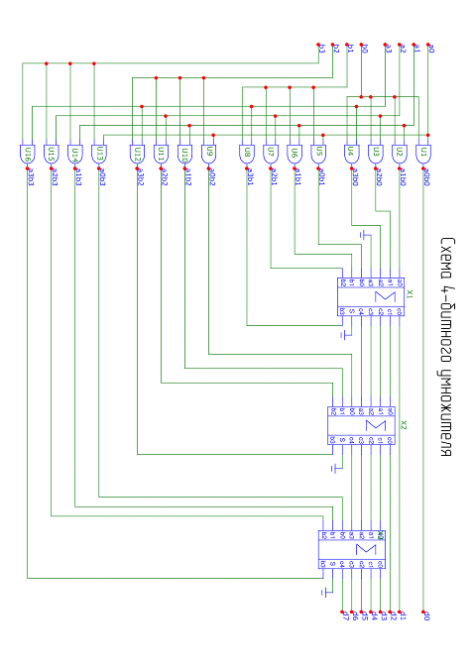

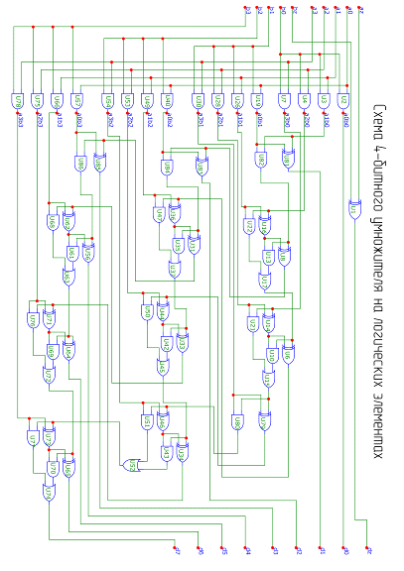

Последовательным соединением получаем схему умножителя (рис. 6). Схема на логических элементах представлена на рисунке 7.

Знаки входных чисел подаются на отдельные входы (az, bz). Вычисление знака реализовано на логическом элементе ИСКЛ-ИЛИ.

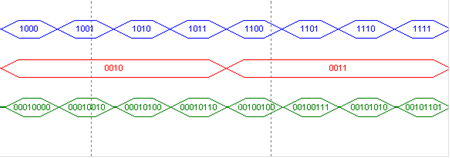

Для проверки работоспособности спроектированного устройства была построена временная диаграмма, её часть приведена на рисунке 8.

Рис. 8. Временная диаграмма спроектированного умножителя

последовательный умножитель число логический

Лучшие статьи по информатике

Проектная компоновка управляющих вычислительных комплексов

Целью курсового проекта является ознакомление с

техническим обеспечением РСУ на базе программно-технических комплексов (ПТК),

включающих контроллеры ра ...

Расчет цифровой радиорелейной линии связи

Линии радиорелейной связи - современный и

перспективный для дальнейшего развития, способ передачи информации на большие

расстояния. Применение радиорелейных ...

Программно управляемый генератор сигнала типа меандр сверхнизкой частоты на микроконтроллере

является

8-ми разрядным CMOS микроконтроллером с низким уровнем энергопотребления,

основанным на усовершенствованной AVR RISC архитектуре. Благодаря выполне ...

Меню сайта

- Главная

- Проектирование современных устройств

- Разработка схем цифровых устройств

- Современные датчики положения

- Современные сетевые технологии

- Современные системы видеонаблюдения

- Телекоммуникационные системы в гостиницах

2026 © www.informaticspoint.ru