Informatics Point

Информатика и проектирование

Входное буферное устройство

Как было установлено в предыдущем разделе, в схеме необходимо буферное устройство, которое должно согласовать диапазон входных напряжений измеряемого сигнала с диапазоном входных напряжений АЦП.

Существуют две очевидных схемы, по которым можно реализовать входной делитель:

. Пассивный резистивный делитель, высокое входное сопротивление которого обеспечивается номиналами сопротивлений;

. Активный делитель на операционном усилителе (ОУ), высокое входное сопротивление которого обеспечивается применением ОУ с полевыми транзисторами на входе и соответствующей схемой включения.

Сначала рассмотрим схему резистивного делителя, как наиболее простую (рис. 3.2).

Рис. 3.2 Резистивный делитель

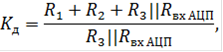

Коэффициент деления в этой схеме равен

а входное сопротивление

![]()

откуда

![]()

![]()

![]()

![]()

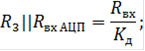

При ![]()

![]() (Uп = 5 В) имеем

(Uп = 5 В) имеем

![]()

![]()

при ![]()

![]() (Uп = 3 В)

(Uп = 3 В)

![]()

![]()

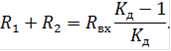

Так как сопротивление ![]()

![]() примерно в 100 раз больше

примерно в 100 раз больше ![]()

![]() , им при расчётах можно пренебречь, а небольшую погрешность коэффициента деления скорректировать подстроечным резистором R2.

, им при расчётах можно пренебречь, а небольшую погрешность коэффициента деления скорректировать подстроечным резистором R2.

Таким образом, схема рис. 3.2 удовлетворяет условиям технического задания. Более сложную схему с применением ОУ не рассматриваем.

Лучшие статьи по информатике

Ремонт и диагностика смартфонов HTC

Смартфон

(англ. smartphone - умный телефон) - мобильный телефон, дополненный

функциональностью карманного персонального компьютера.

Смартфоны

отличаются от ...

Технология ZigBee

автоматизация дом безопасность умный

В самых разных отраслях имеется потребность в создании беспроводных сетей

с большим числом датчиков и исполнительных меха ...

Проект цифрового печатного узла, выполняющего функцию стабилизации напряжения

Производство

цифровых устройств электронной аппаратуры в настоящее время находит все более

широкое применение во многих областях народного хозяйства и в зна ...

Меню сайта

- Главная

- Проектирование современных устройств

- Разработка схем цифровых устройств

- Современные датчики положения

- Современные сетевые технологии

- Современные системы видеонаблюдения

- Телекоммуникационные системы в гостиницах

2026 © www.informaticspoint.ru