Informatics Point

Информатика и проектирование

Синтез схемы делителя частоты

Делитель частоты служит для уменьшения частоты импульсов источника цифровых импульсов (генератора тактовых импульсов) в Кд раз. Здесь Кд - коэффициент делителя частоты.

Частота выходных импульсов делителя частоты:

fвых = fвх / Кд,

где fвх - частота генератора тактовых импульсов на входе делителя частоты.

Схема делителя частоты строится по принципу асинхронных счетных схем и состоит из n триггеров, соединенных последовательно. Число триггеров в схеме и Кд связаны соотношением

n ≥ Кд.

Рассмотрим пример построения схемы делителя частоты на D-триггерах и Кд = 26.

4<26<25 (16<26<32)

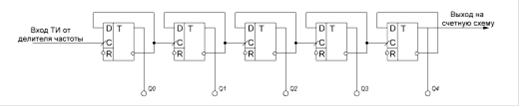

В данном случае схема состоит из пяти D-триггеров и комбинационной схемы. Так как D-триггер имеет инверсный вход сброса (вход R), то активным сигналом сброса является логический ноль. Для организации смены состояний триггеров в момент прихода очередного импульса на тактовый (счетный) вход триггера младшего разряда их инверсные выходы должны быть соединены с D-входом. Для организации асинхронной передачи информации инверсные выходы триггеров нулевого, первого и второго разрядов необходимо соединить с тактовыми входами триггеров соответственно первого, второго и третьего разрядов, т. е. по принципу построения схемы суммирующего счетчика (рис. 7).

Рис.7

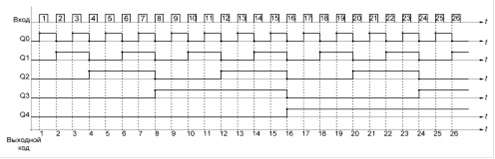

Представим временные диаграммы на входе делителя частоты и на каждом прямом выходе триггеров (рис.8)

Рис.8

Максимальное значение Кд схемы на рис.8 равно 32, т.е. модулю асинхронного счетчика, построенного на пяти D-триггерах, так как 25= 32. Для получения значения Кд= 26 необходимо изменить (уменьшить) модуль счета путем обнуления всех разрядов в момент прихода 26-го импульса. Для этого служит комбинационная схема, реализующая функцию обнуления триггеров. Для определения вида этой функции и реализации ее запишем значение Кд в виде 5-разрядного двоичного числа: 2610= 110102. Каждый разряд этого числа поставим в соответствие со значением прямого или инверсного выхода триггеров, т.е. Q4=1 Q3=1; Q2=0; Q1=1; Q0=0.

Функция обнуления триггеров будет иметь вид:

![]() .

.

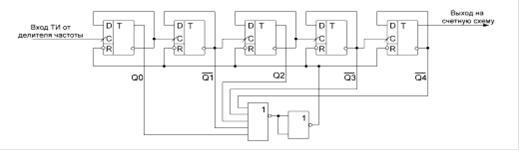

Тогда комбинационная схема, реализуемая на основе этой ФАЛ, будет состоять из 5-входового логического элемента типа 5ИЛИ-НЕ (рис.9).

Рис.9

Лучшие статьи по информатике

Нелинейный локатор

Большинство людей, которые мало знакомы с особенностями технического

шпионажа, полагают, что подслушивающие устройства представляют собой

исключительно ради ...

Электронавигационные приборы

На каждом судне для следования по намеченному курсу, выбора пути

следования, контроля местонахождения в открытом море с учетом изменяющейся

навигационной и ...

Разработка технологического процесса сборки и монтажа усилителя тока

В

настоящее время, когда развивающаяся рыночная экономика заставляет предприятия

специализирующиеся на выпуске радиоэлектронной аппаратуры (РЭА) работать в

...

Меню сайта

- Главная

- Проектирование современных устройств

- Разработка схем цифровых устройств

- Современные датчики положения

- Современные сетевые технологии

- Современные системы видеонаблюдения

- Телекоммуникационные системы в гостиницах

2026 © www.informaticspoint.ru