Informatics Point

Информатика и проектирование

Краткое описание микросхем

Логическое сложение (дизъюнкция) является функцией (у) переменных (х1, х2, . ., хn) и фиксирует наступление сложного события (у=1), если наступило хотя бы одно простое событие (x1 = 1 ИЛИ х2= 1 . ИЛИ хn=1). Отсюда следует еще одно название рассматриваемой операции - операция ИЛИ. Элемент ИЛИ изображен на рисунке 2.

Рис. 2

Логическое отрицание (инверсия) записывается в виде у=![]() и называется также операцией НЕ (читается «у НЕ х»). Элемент НЕ изображен на рисунке 3.

и называется также операцией НЕ (читается «у НЕ х»). Элемент НЕ изображен на рисунке 3.

Рис. 3

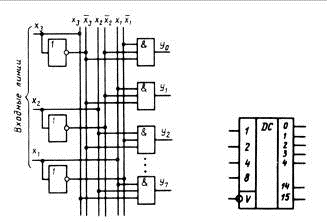

Дешифратор. Каждому цифровому коду на входах дешифратора соответствует логическая 1 (или логический 0) на соответствующем выходе. Так, на одном выходе дешифратора появляется логическая 1, а на остальных - логические 0, когда на входах устанавливается, к примеру, двоичный код десятичного числа четырех; логическая 1 на другом выходе и логические 0 на остальных появляются, когда на входах присутствует двоичный код десятичного числа пяти и т. д. Таким образом, дешифратор расшифровывает (дешифрирует), число, записанное в двоичном коде, представляя его логической 1 (логическим 0) на определенном выходе. Структура дешифратора показана на рисунке 4а, условное изображение дешифратора на рисунке 4б.

Рис. 4

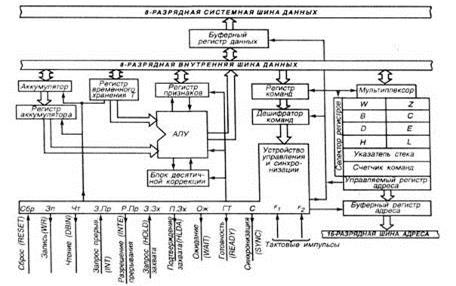

Микропроцессор - единственный активный элемент МП-системы. Он управляет выполнением программы, осуществляя необходимые преобразования информации, обеспечивает управление всеми компонентами системы, передачу информации между ними, а также между системой и периферийными устройствами. Структура МП показана на рисунке 5а, условное изображение МП на рисунке 5б.

Рис. 5

Запоминающие устройства (ЗУ) предназначены для хранения информации, выраженной двоичными числами. Такая информация заносится (записывается) в ЗУ и в нужные моменты из него выбирается (считывается).

Запоминающее устройство - один из основных функциональных блоков электронных вычислительных машин; в нем хранятся числа, над которыми должны быть произведены определенные действия, и числа - коды команд, определяющие характер этих действий.

Запоминающее устройство состоит из запоминающего массива и электронного обрамления. Запоминающий массив (накопитель) содержит запоминающие элементы (ЗЭ), каждый из которых может принимать состояния лог. 1 и лог. О, т. е. хранить один бит информации. В запоминающем элементе хранится один разряд записанного двоичного слова; все n-разрядное слово заносится в запоминающие элементы, составляющие ячейку памяти.

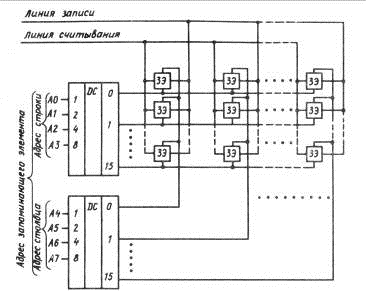

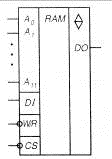

ЗУ с одноразрядной организацией. В этом случае ЗУ имеет матрицу, каждый запоминающий элемент которой выбирается дешифратором строки и дешифратором столбца. Выбранным оказывается элемент, находящийся на пересечении возбужденных линий, одна из которых принадлежит дешифратору строки, а другая - дешифратору столбца. Структура этого ЗУ показана на рисунке 6а, его условное изображение на рисунке 6б.

Рис. 6

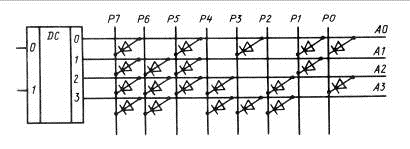

Элементами ПЗУ в нашем случае являются диоды . На рис. 7а, а изображено матричное ПЗУ, состоящее из диодной матрицы и внутреннего дешифратора адреса. Горизонтальные линии матрицы - адресные; вертикальные - разрядные, с них снимаются восьмиразрядные двоичные числа, записанные в ПЗУ. Код адреса возбуждает одну из адресных линий матрицы. Диоды в ней расположены так, чтобы обеспечить соединение адресуемой линии с теми разрядными линиями, на которых нужно получить лог. 1. Условное изображение ПЗУ представлено на рис. 7б.

Рис. 7

Программируемый параллельный интерфейс (ППИ).

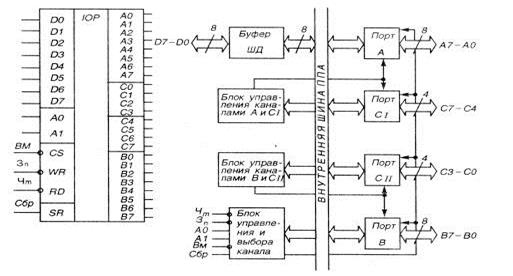

ППИ (иначе- программируемый параллельный периферийный адаптер - ППА) позволяет осуществлять обмен данными в параллельном формате между МП и практически любым внешним устройством.

Порты А и В - 8-разрядные регистры всегда работают как порты (каналы) вводы-вывода. В них заносятся данные ВУ для передачи в МП или наоборот. Порты С1 и С2 содержат 4-разрядные регистры и тоже могут работать на ввод или вывод как один 8-разрядный порт, как два независимых 4-разрядных порта, а также могут обеспечивать управляющими сигналами обмен данными через порты А и В. Структура ППИ показана на рисунке 8б, условное изображение ППИ на рисунке 8а.

Рис. 8

Генератор тактовых импульсов. Основное назначение генератора тактовых импульсов (ГТИ) - формирование двух непересекающихся во времени серий положительных тактовых импульсов с определенными параметрами, и временная привязка к ним сигналов, управляющих работой микропроцессора. Условное изображение генератора тактовых импульсов приведена на рис. 9.

Лучшие статьи по информатике

Цифровой таймер для насоса

Устройства способные облегчить жизнь в быту, уже давно заполнили наши

дома. Данное устройство, как раз одно из таких, и предназначено для

периодического зап ...

Разработка интегрированной системы управления отделением разваривания на спиртзаводе на основе программируемого логического контроллера Modicon TSX Momentum

Автоматизация технологических процессов - этап комплексной механизации,

характеризуемый освобождением человека от непосредственного выполнения функций

управ ...

Проектирование специализированного вычислительного устройства

Эффективность применения современных средств вычислительной техники во

всех сферах научной и производственной деятельности оказывает решающее влияние

на уве ...

Меню сайта

- Главная

- Проектирование современных устройств

- Разработка схем цифровых устройств

- Современные датчики положения

- Современные сетевые технологии

- Современные системы видеонаблюдения

- Телекоммуникационные системы в гостиницах

2026 © www.informaticspoint.ru