Informatics Point

Информатика и проектирование

Разработка схемы регистровой памяти на базе двух 3-разрядных регистров, информация на входной шине адреса - 010, на входной шине данных - 210

Регистровая память - registerfile - это сверхоперативное запоминающее устройство (СОЗУ) - схема из нескольких регистров, предназначенная для хранения нескольких многоразрядных слов.

Данное СОЗУ имеет информационный объем 6 бит. Здесь DI - datainput - входная шина данных, DO - dataoutput - выходная шина данных, WR - сигнал записи в СОЗУ, RD - сигнал чтения информации из СОЗУ, ВШД - внутренняя шина данных.

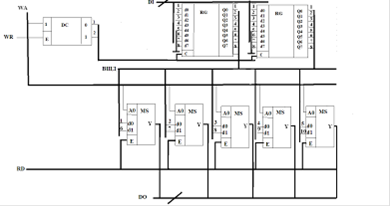

На рисунке 2.13 представлена схема регистровой памяти.

Каждый регистр имеет одноразрядный адрес, который подается на входы дешифратора.

Рисунок 2.13 Схема регистровой памяти

При наличии активного сигнала записи WR = 1 на дешифратор DD1 подается значение 0. Это приводит к появлению значения 1 на выходе 1, который по шине подается на синхронизирующий вход регистра 2. Следовательно, активным будет только второй регистр. С шины данных на его вход d1 подается 0 , а на d0 - 1. В результате на выходе Q1 будет значение 1.

При активном сигнале чтения RD = 1 активизируются все 2 мультиплексора, поскольку на их разрешающие входы подан активный сигнал Е = 1. В соответствии с поданным на дешифратор адресом мультиплексоры коммутируют на выходную шину данных информацию с регистра 3.

Выводы: разработана схема регистровой памяти с пятиразрядной шиной данных, использовано два регистра. Изучен принцип работы регистров. Углублены знания о строении регистровой памяти.

Заключение

В результате выполнения данной курсовой работы мною были выполнены все поставленные задания. Также подробно рассмотрены принципы функционирования элементов последовательного и комбинационного типа. В процессе работы были использованы элементы логики, дешифраторы, мультиплексоры, триггеры, регистры. Так же были построены схемы концептуального и функционального уровня. Для построения схем концептуального уровня использовали компонент Microsoft - Paint, Corel Draw, а для функционального уровня NI Multisim 10. Я использовала Multisim10 для того что бы наглядно показать интерфейс, а так же для графического анализа результатов моделирования. Для разработки схемы каскадного соединения мультиплексоров был использован 1 мультиплексор 74153N, а для схемы каскадного соединения дешифраторов -5 дешифраторов 74LS139D.

Лучшие статьи по информатике

Характеристика аппаратуры на ООО Заполярпромгражданстрой

В соответствии с учебным планом я проходил учебную практику в

обществе с ограниченной ответственностью «Заполярпромгражданстрой» с 22 апреля

2013 года по 12 ...

Проектирование телевизионного приемника

электрический напряжение приемник телевизионный

Цель курсового проекта: закрепить знания,

полученные при изучении теоретической части дисциплины, привить навы ...

Применение цифровых фотокамер для осуществления регулярной видеосъемки в образовательных учреждениях

цифровая фотокамера видеосъёмка

Современная

жизнь диктует новые требования к качеству изобразительного контента. Если в

1980-90 е года черно-белая картинка с ...

Меню сайта

- Главная

- Проектирование современных устройств

- Разработка схем цифровых устройств

- Современные датчики положения

- Современные сетевые технологии

- Современные системы видеонаблюдения

- Телекоммуникационные системы в гостиницах

2026 © www.informaticspoint.ru